CPU

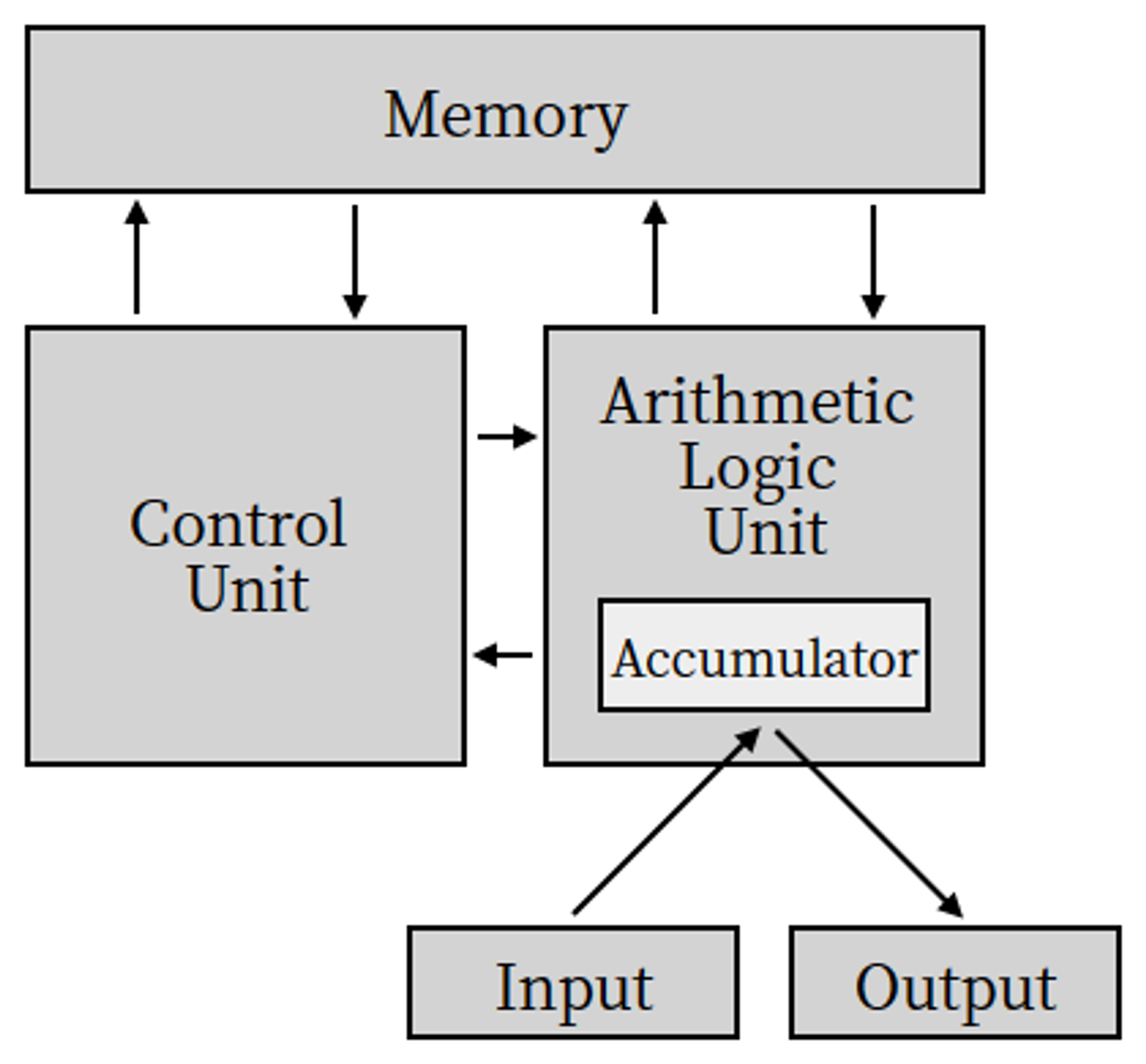

计算机基本结构

计算机基本结构为 5 个部分,分别是运算器、控制器、存储器、输入设备、输出设备,这 5 个部分也被称为冯诺依曼模型

CPU

中央处理器也就是我们常说的 CPU,32 位和 64 位 CPU 最主要区别在于一次能计算多少字节数据:

- 32 位 CPU 一次可以计算 4 个字节;

- 64 位 CPU 一次可以计算 8 个字节;

这里的 32 位和 64 位,通常称为 CPU 的位宽,代表的是 CPU 一次可以计算(运算)的数据量。

之所以 CPU 要这样设计,是为了能计算更大的数值,如果是 8 位的 CPU,那么一次只能计算 1 个字节

0~255 范围内的数值,这样就无法一次完成计算 10000 * 500 ,于是为了能一次计算大数的运算,CPU 需要支持多个 byte 一起计算,所以 CPU 位宽越大,可以计算的数值就越大,比如说 32 位 CPU 能计算的最大整数是 4294967295。常见的寄存器种类:

- 通用寄存器,用来存放需要进行运算的数据,比如需要进行加和运算的两个数据。

- 程序计数器,用来存储 CPU 要执行下一条指令「所在的内存地址」,注意不是存储了下一条要执行的指令,此时指令还在内存中,程序计数器只是存储了下一条指令「的地址」。

- 指令寄存器,用来存放当前正在执行的指令,也就是指令本身,指令被执行完成之前,指令都存储在这里。

总线

总线是用于 CPU 和内存以及其他设备之间的通信,总线可分为 3 种:

- 地址总线,用于指定 CPU 将要操作的内存地址;

- 数据总线,用于读写内存的数据;

- 控制总线,用于发送和接收信号,比如中断、设备复位等信号,CPU 收到信号后自然进行响应,这时也需要控制总线;

位宽

知道了线路位宽的意义后,我们再来看看 CPU 位宽。

CPU 的位宽最好不要小于线路位宽,比如 32 位 CPU 控制 40 位宽的地址总线和数据总线的话,工作起来就会非常复杂且麻烦,所以 32 位的 CPU 最好和 32 位宽的线路搭配,因为 32 位 CPU 一次最多只能操作 32 位宽的地址总线和数据总线。

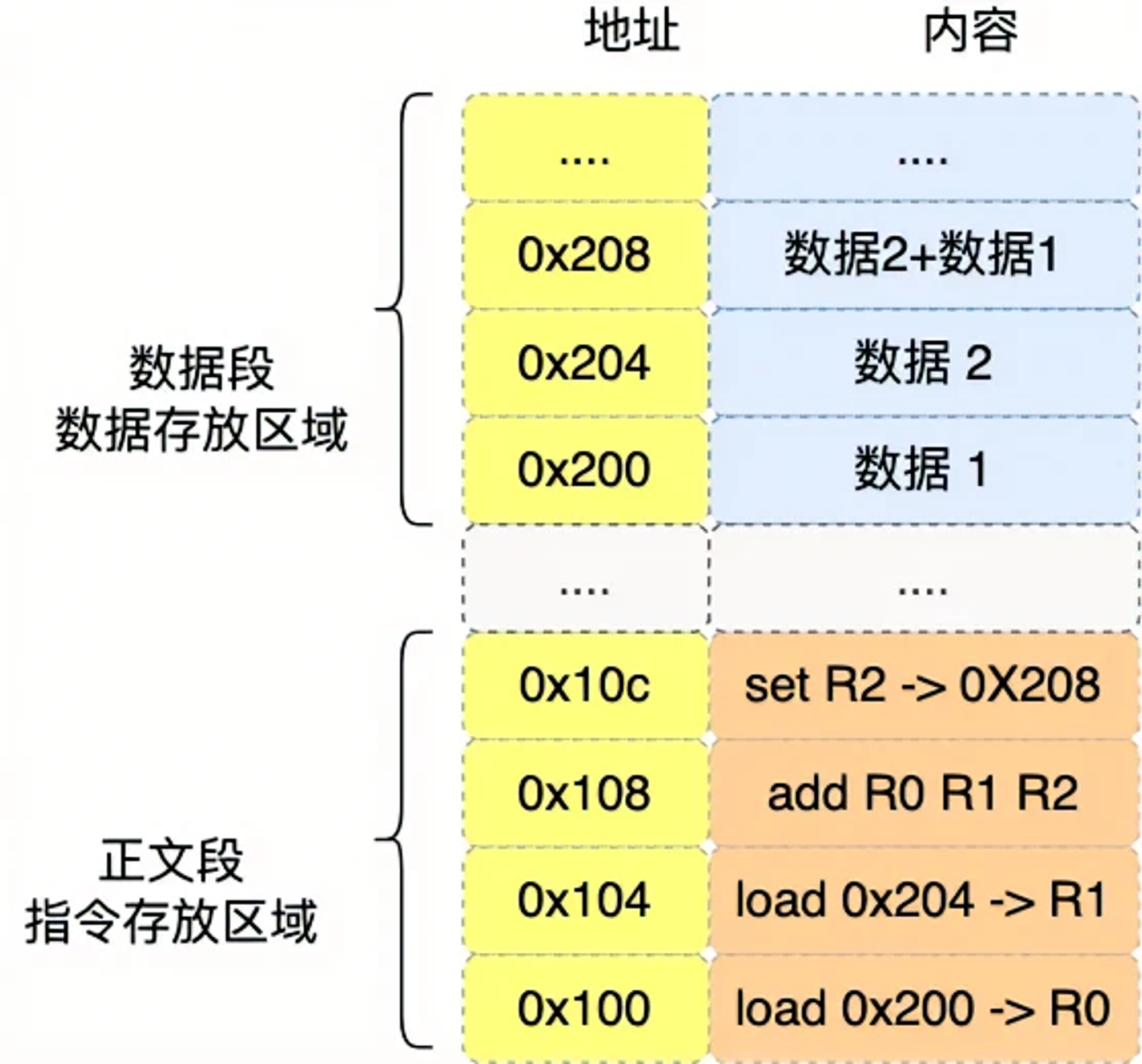

执行流程和示例

那 CPU 执行程序的过程如下:

- 第一步,CPU 读取「程序计数器」的值,这个值是指令的内存地址,然后 CPU 的「控制单元」操作「地址总线」指定需要访问的内存地址,接着通知内存设备准备数据,数据准备好后通过「数据总线」将指令数据传给 CPU,CPU 收到内存传来的数据后,将这个指令数据存入到「指令寄存器」。

- 第二步,「程序计数器」的值自增,表示指向下一条指令。这个自增的大小,由 CPU 的位宽决定,比如 32 位的 CPU,指令是 4 个字节,需要 4 个内存地址存放,因此「程序计数器」的值会自增 4;

- 第三步,CPU 分析「指令寄存器」中的指令,确定指令的类型和参数,如果是计算类型的指令,就把指令交给「逻辑运算单元」运算;如果是存储类型的指令,则交由「控制单元」执行;

a = 1 + 2的示例:

指令

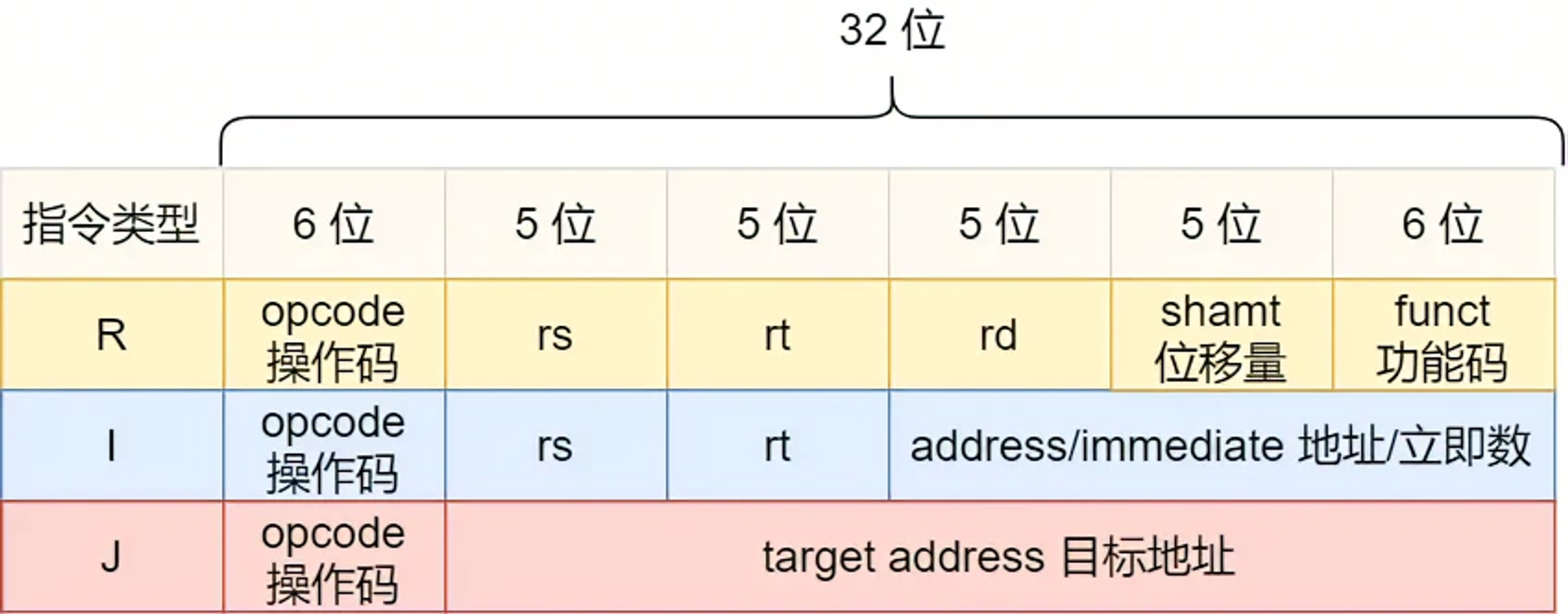

MIPS

- R 指令(寄存器),用在算术和逻辑操作,里面有读取和写入数据的寄存器地址。如果是逻辑位移操作,后面还有位移操作的「位移量」,而最后的「功能码」则是再前面的操作码不够的时候,扩展操作码来表示对应的具体指令的;

- I 指令(立即数),用在数据传输、条件分支等。这个类型的指令,就没有了位移量和功能码,也没有了第三个寄存器,而是把这三部分直接合并成了一个地址值或一个常数;

- J 指令(跳转),用在跳转,高 6 位之外的 26 位都是一个跳转后的地址;

示例

R指令格式:R指令(即寄存器指令)主要由三个操作数组成,分别表示源寄存器1、源寄存器2和目的寄存器。例如:ADD R1, R2, R3 表示将寄存器R2和寄存器R3中的值相加,并将结果存储到寄存器R1中。

I指令格式:I指令(即立即数指令)主要由两个操作数组成,其中一个是寄存器,另一个是一个立即数。例如:ADDI R1, R2, #10 表示将寄存器R2中的值和10相加,并将结果存储到寄存器R1中。

J指令格式:J指令(即跳转指令)主要用于程序跳转,只有一个操作数,表示跳转的目标地址。例如:JMP #100 表示跳转到指令地址为100的位置执行。

流水线

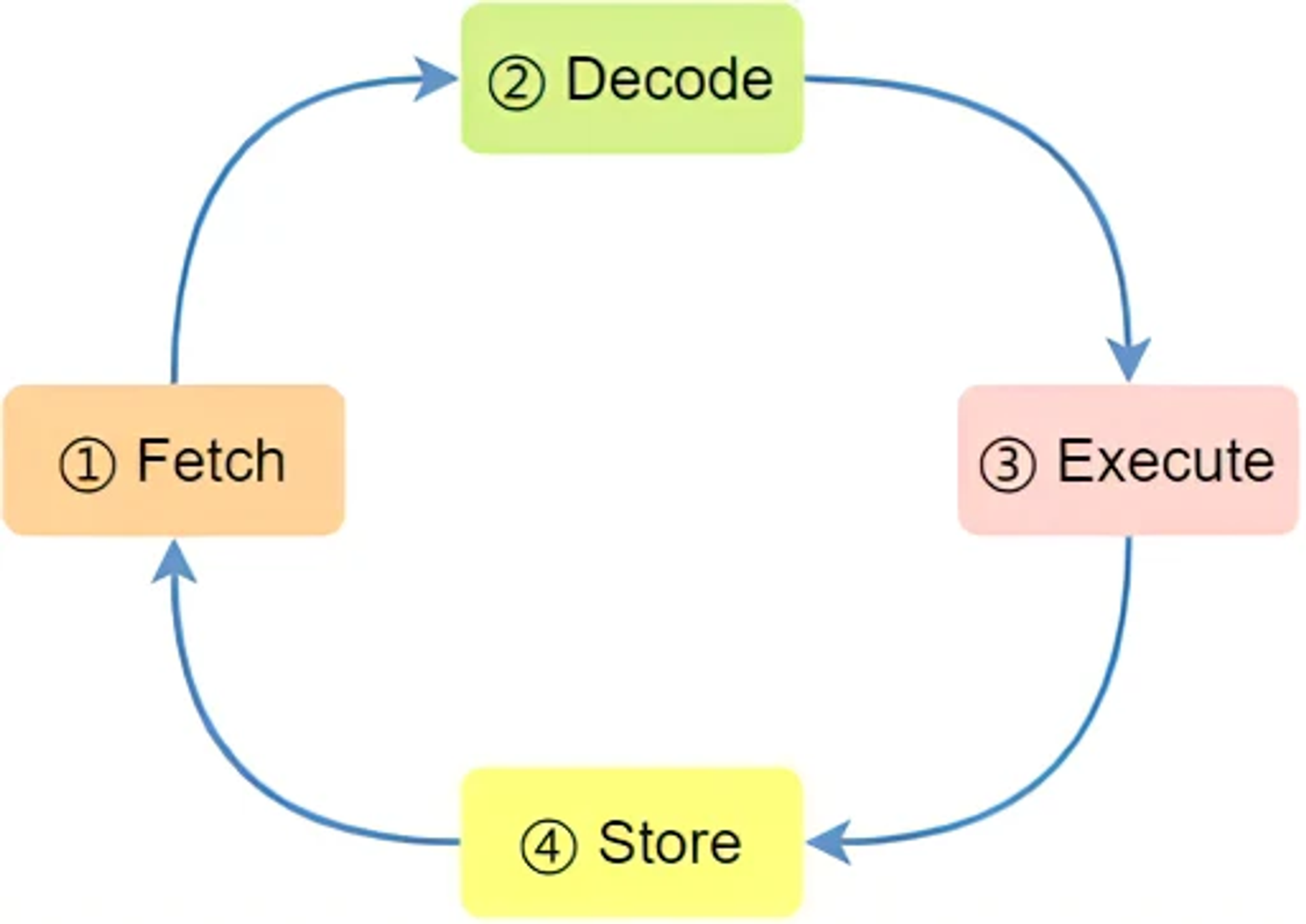

指令执行按照流水线:

四个阶段的具体含义:

- CPU 通过程序计数器读取对应内存地址的指令,这个部分称为 Fetch(取得指令);

- CPU 对指令进行解码,这个部分称为 Decode(指令译码);

- CPU 执行指令,这个部分称为 Execution(执行指令);

- CPU 将计算结果存回寄存器或者将寄存器的值存入内存,这个部分称为 Store(数据回写);

上面这 4 个阶段,我们称为指令周期(Instrution Cycle),CPU 的工作就是一个周期接着一个周期,周而复始。

分类

指令从功能角度划分,可以分为 5 大类:

- 数据传输类型的指令,比如

store/load是寄存器与内存间数据传输的指令,mov是将一个内存地址的数据移动到另一个内存地址的指令;

- 运算类型的指令,比如加减乘除、位运算、比较大小等等,它们最多只能处理两个寄存器中的数据;

- 跳转类型的指令,通过修改程序计数器的值来达到跳转执行指令的过程,比如编程中常见的

if-else、switch-case、函数调用等。

- 信号类型的指令,比如发生中断的指令

trap;

- 闲置类型的指令,比如指令

nop,执行后 CPU 会空转一个周期;

执行时间

- 指令数,表示执行程序所需要多少条指令,以及哪些指令。这个层面是基本靠编译器来优化,毕竟同样的代码,在不同的编译器,编译出来的计算机指令会有各种不同的表示方式。

- 每条指令的平均时钟周期数 CPI,表示一条指令需要多少个时钟周期数,现代大多数 CPU 通过流水线技术(Pipeline),让一条指令需要的 CPU 时钟周期数尽可能的少;

- 时钟周期时间,表示计算机主频,取决于计算机硬件。有的 CPU 支持超频技术,打开了超频意味着把 CPU 内部的时钟给调快了,于是 CPU 工作速度就变快了,但是也是有代价的,CPU 跑的越快,散热的压力就会越大,CPU 会很容易奔溃。

64位 VS 32位

64 位相比 32 位 CPU

64 位相比 32 位 CPU 的优势主要体现在两个方面:

- 64 位 CPU 可以一次计算超过 32 位的数字,而 32 位 CPU 如果要计算超过 32 位的数字,要分多步骤进行计算,效率就没那么高,但是大部分应用程序很少会计算那么大的数字,所以只有运算大数字的时候,64 位 CPU 的优势才能体现出来,否则和 32 位 CPU 的计算性能相差不大。

- 通常来说 64 位 CPU 的地址总线是 48 位,而 32 位 CPU 的地址总线是 32 位,所以 64 位 CPU 可以寻址更大的物理内存空间。如果一个 32 位 CPU 的地址总线是 32 位,那么该 CPU 最大寻址能力是 4G,即使你加了 8G 大小的物理内存,也还是只能寻址到 4G 大小的地址,而如果一个 64 位 CPU 的地址总线是 48 位,那么该 CPU 最大寻址能力是

2^48,远超于 32 位 CPU 最大寻址能力。

64 位相比 32 位 软件

64 位和 32 位软件,实际上代表指令是 64 位还是 32 位的:

- 如果 32 位指令在 64 位机器上执行,需要一套兼容机制,就可以做到兼容运行了。但是如果 64 位指令在 32 位机器上执行,就比较困难了,因为 32 位的寄存器存不下 64 位的指令;

- 操作系统其实也是一种程序,我们也会看到操作系统会分成 32 位操作系统、64 位操作系统,其代表意义就是操作系统中程序的指令是多少位,比如 64 位操作系统,指令也就是 64 位,因此不能装在 32 位机器上。

总之,硬件的 64 位和 32 位指的是 CPU 的位宽,软件的 64 位和 32 位指的是指令的位宽。

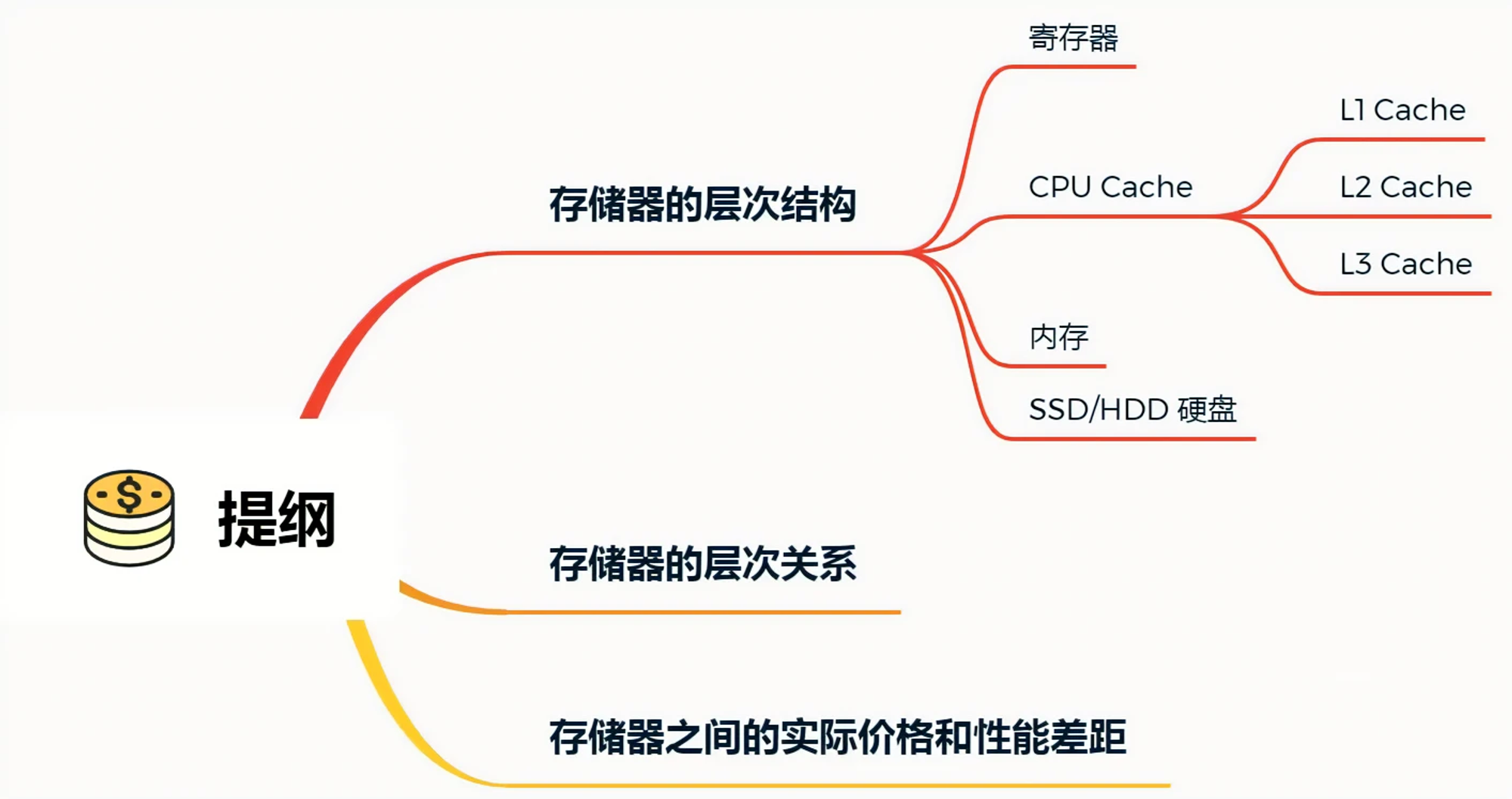

存储和缓冲

基本结构

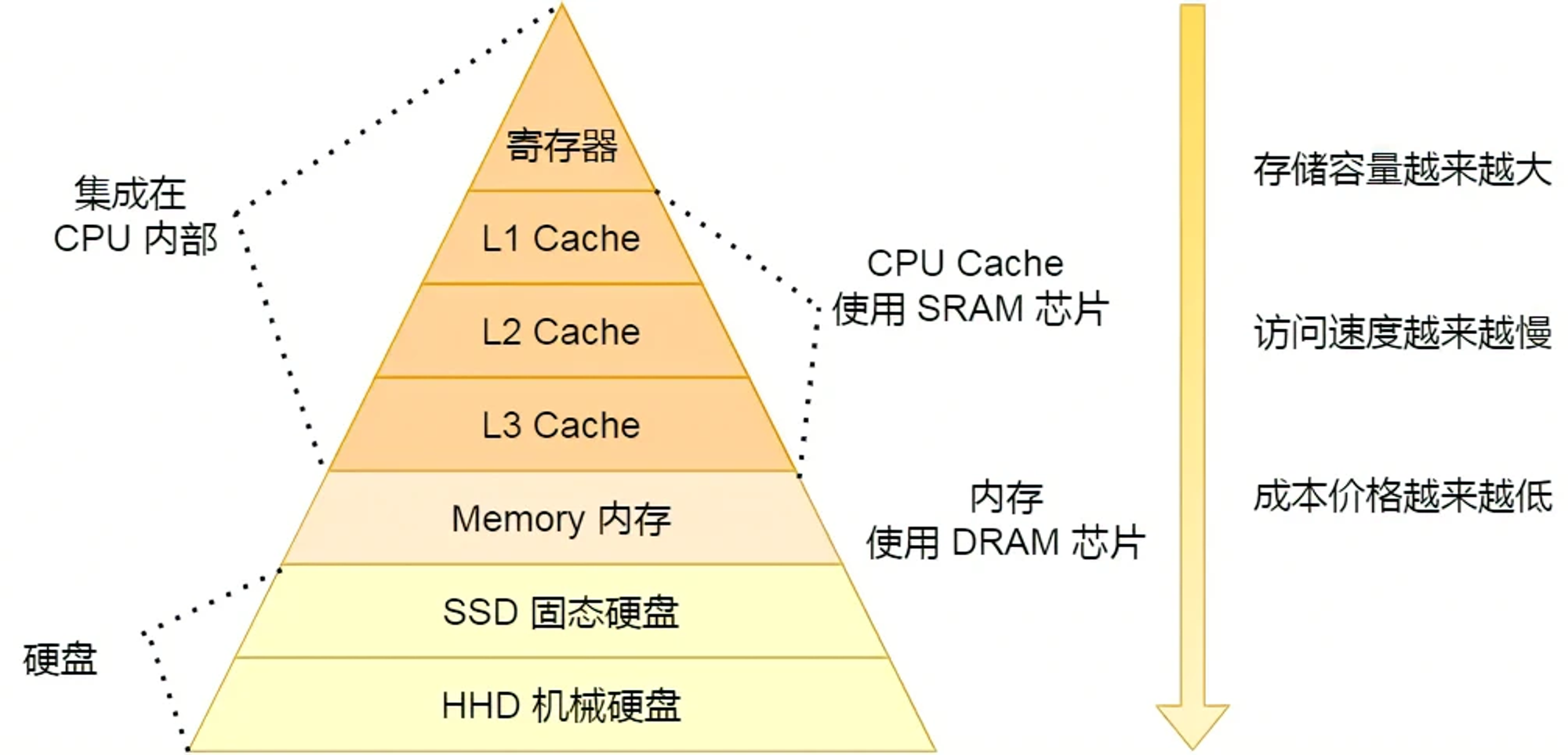

- 寄存器:SRAM。

半个 CPU 时钟周期;0.5ns;几十到几百个。

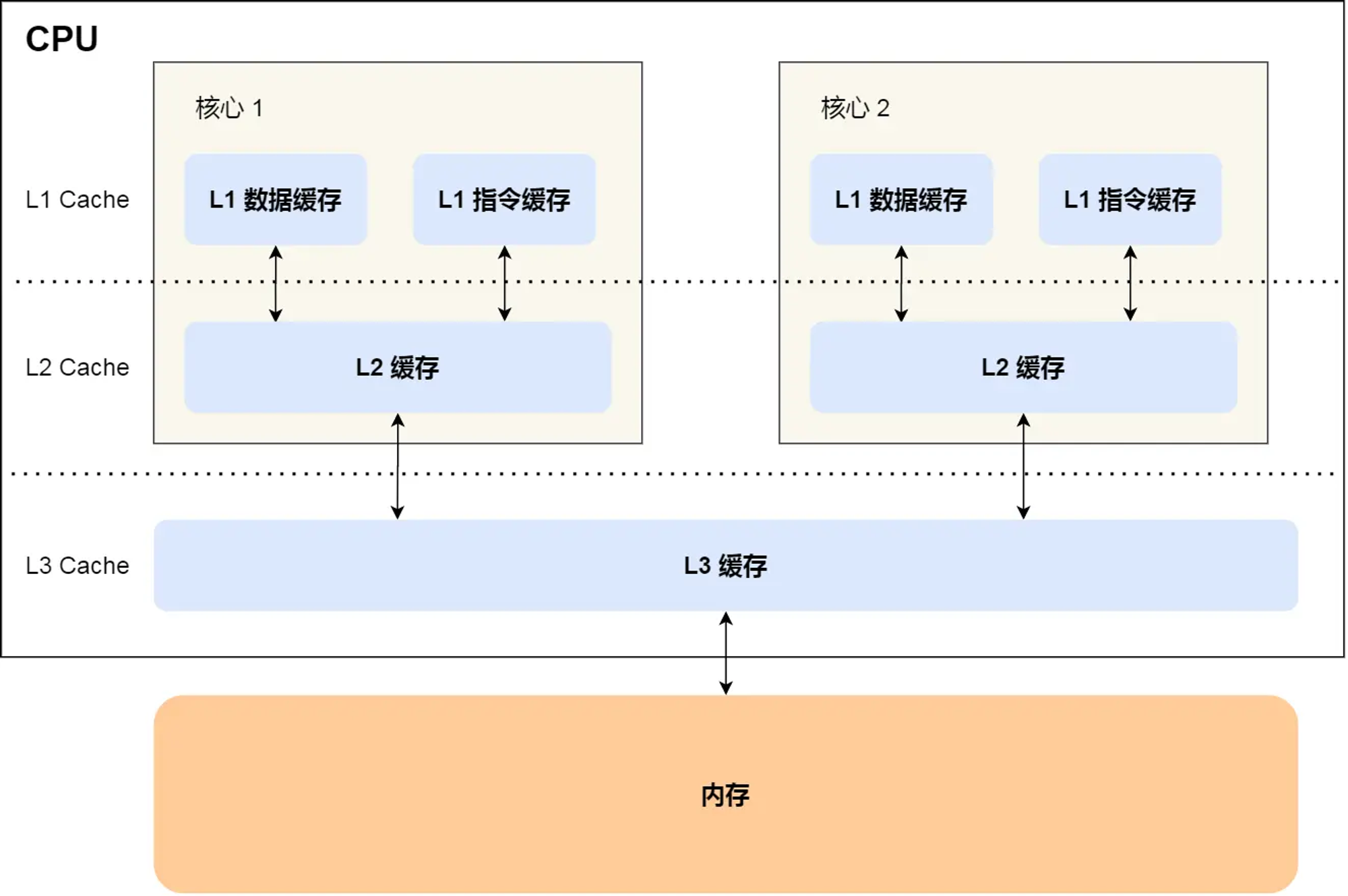

- CPU Cache。SRAM(Static Random-Access Memory,静态随机存储器)。在 SRAM 里面,一个 bit 的数据,通常需要 6 个晶体管,

- L1。通常只需要

2~4个时钟周期,而大小在几十 KB 到几百 KB 不等。所以 L1 高速缓存通常分成指令缓存和数据缓存。 - L2。访问速度则更慢,速度在

10~20 个时钟周期,通常大小在几百 KB 到几 MB 不等。 - L3。访问速度在

20~60个时钟周期。通常是多个 CPU 核心共用的。

- 内存。DRAM (Dynamic Random Access Memory,动态随机存取存储器)。内存速度大概在 200~300 个 时钟周期之间。

DRAM 存储一个 bit 数据,只需要一个晶体管和一个电容就能存储,但是因为数据会被存储在电容里,电容会不断漏电,所以需要「定时刷新」电容,才能保证数据不会被丢失

- 硬盘。SSD/HDD。它的速度比内存慢 10W 倍左右。

总结:

存储器 | 硬件介质 | 访问速度/周期 | 速度/时间 | 大小 | 价格/d/MB |

Register | SRAM | 半个 CPU 时钟周期 | 0.5ns | 几十到几百 | ㅤ |

CPU Cache | SRAM | L1:2-4个周期

L2:10-20个周期

L3:20-60个周期 | L1:1ns

L2:4ns

L3:10ns | L1:几十K;

L2:MB;

L3:很多MB | 7 |

内存 | DRAM | 200-300个周期 | 100ns | GB | 0.015 |

硬盘 | SSD/HDD | 2000,0000个周期 | SSD:150us

HDD:10ms | TB | 0.0004;

0.00004; |

ㅤ | ㅤ | ㅤ | ㅤ | ㅤ | ㅤ |

/

- 作者:Olimi

- 链接:https://olimi.icu/article/b9cf4bdd-97f0-49c2-8db3-46f4eb04944c

- 声明:本文采用 CC BY-NC-SA 4.0 许可协议,转载请注明出处。